#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re the Application of

Tsuyoshi TAMURA

Application No.:

Filed: July 25, 2001

Docket No.:

Group Art Unit:

110195

2673

For:

RAM-INCORPORATED DRIVER, AND DISPLAY UNIT AND ELECTRONIC

EQUIPMENT USING THE SAME

#### **CLAIM FOR PRIORITY**

Director of the U.S. Patent and Trademark Office Washington, D.C. 20231

Sir:

The benefit of the filing dates of the following prior foreign applications filed in the following foreign country is hereby requested for the above-identified patent application and the priority provided in 35 U.S.C. §119 is hereby claimed:

Japanese Patent Application No. 11-338146 filed November 29, 1999 and Japanese Patent Application No. 2000-211080 filed July 12, 2000.

SEP 2 0 2001

In support of this claim, certified copies of said original foreign applications:

| X | are filed herewith.                          |

|---|----------------------------------------------|

|   | were filed on in Parent Application No filed |

|   | will be filed at a later date.               |

It is requested that the file of this application be marked to indicate that the requirements of 35 U.S.C. §119 have been fulfilled and that the Patent and Trademark Office kindly acknowledge receipt of these documents.

Respectfully submitted,

James A. Oliff

Registration No. 27,075

Thomas J. Pardini Registration No. 30,411

JAO:TJP/kaf

Date: September 20, 2001

OLIFF & BERRIDGE, PLC P.O. Box 19928 Alexandria, Virginia 22320 Telephone: (703) 836-6400

DEPOSIT ACCOUNT USE **AUTHORIZATION** Please grant any extension necessary for entry; Charge any fee due to our Deposit Account No. 15-0461

# 本 国 特 許 庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日 Date of Application:

2000年 7月12日

出 願 番 号

Application Number:

特願2000-211080

出 願 人 Applicant(s):

セイコーエプソン株式会社

CERTIFIED COPY OF PRIORITY DOCUMENT

2001年 8月17日

特 許 庁 長 官 Commissioner, Japan Patent Office

【書類名】

特許願

【整理番号】

EP-0267201

【提出日】

平成12年 7月12日

【あて先】

特許庁長官殿

【国際特許分類】

G09G 3/36

H04N 5/66

【発明者】

【住所又は居所】

長野県諏訪市大和3丁目3番5号 セイコーエプソン株

式会社内

【氏名】

田村 剛

【特許出願人】

【識別番号】

000002369

【氏名又は名称】 セイコーエプソン株式会社

【代理人】

【識別番号】

100090479

【弁理士】

【氏名又は名称】

井上 一

【電話番号】

03-5397-0891

【選任した代理人】

【識別番号】

100090387

【弁理士】

【氏名又は名称】 布施 行夫

【電話番号】

03-5397-0891

【選任した代理人】

【識別番号】

100090398

【弁理士】

【氏名又は名称】 大渕 美千栄

【電話番号】

03-5397-0891

【先の出願に基づく優先権主張】

【出願番号】

平成11年特許願第338146号

【出願日】

平成11年11月29日

【手数料の表示】

【予納台帳番号】

039491

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 9402500

【プルーフの要否】

要

# 【書類名】 明細書

【発明の名称】 RAM内蔵ドライバ並びにそれを用いた表示ユニットおよび電子機器

# 【特許請求の範囲】

【請求項1】 静止画データおよび動画データに基づいて表示部を表示駆動 するRAM内蔵ドライバであって、

それぞれ前記静止画データおよび動画データを伝送するための第1および第2 のバスラインと、

前記第1および第2のバスラインを介して伝送された前記静止画データおよび 動画データを記憶するRAMと、

所与のコマンドに基づいて、前記RAMに対し、前記第1又は第2のバスラインを介してそれぞれ別個に伝送された前記静止画データ又は動画データの書き込み又は読み出し制御する第1の制御回路と、

前記第1の制御回路とは独立して、前記RAMに記憶された前記静止画データ 又は動画データを表示データとして読み出し制御し、前記表示部を表示駆動する 第2の制御回路と、

を含むことを特徴とするRAM内蔵ドライバ。

【請求項2】 請求項1において、

前記RAMは、前記第1のバスラインを介して前記静止画データの書き込みが行われる第1のポートと、前記第2のバスラインを介して前記動画データの書き込みが行われる第2のポートと、前記表示データを読み出すための第3のポートとを有するメモリセルを含むことを特徴とするRAM内蔵ドライバ。

【請求項3】 外部MPUからのコマンド、静止画データおよび動画データに基づいて表示部を表示駆動するRAM内蔵ドライバであって、

前記外部MPUからの前記静止画データを伝送する第1のバスラインと、

前記外部MPUからの前記動画データを伝送する第1のバスラインと、

前記静止画データおよび前記動画データを記憶するRAMと、

前記静止画データを書き込むための前記RAMのカラムアドレスを指定する第

1のカラムアドレス制御回路と、

前記動画データを書き込むための前記RAMのカラムアドレスを指定する第2のカラムアドレス制御回路と、

前記静止画データを書き込むための前記RAMのページアドレスを指定する第 1のページアドレス制御回路と、

前記動画データを書き込むための前記RAMのページアドレスを指定する第2のページアドレス制御回路と、

前記外部MPUからの前記コマンドに基づいて、前記第1、第2のカラムアドレス制御回路および前記第1、第2のページアドレス制御回路を制御するMPU系制御回路と、

前記RAMに記憶された前記静止画データおよび前記動画データを、表示データとして読み出し制御する表示アドレス制御回路と、

前記MPU系制御回路とは独立して、前記表示アドレス制御回路を制御するドライバ系制御回路と、

を有することを特徴とするRAM内蔵ドライバ。

【請求項4】 請求項3において、

前記RAMのメモリセルに接続された第1の一対のビット線と、

前記RAMのメモリセルに接続された第2の一対のビット線と、

前記第1のカラムアドレス制御回路に制御されて前記第1の一対のビット線と 前記第1のバスラインとを接続する第1のカラムスイッチと、

前記第2のカラムアドレス制御回路に制御されて前記第2の一対のビット線と 前記第2のバスラインとを接続する第2のカラムスイッチと、

前記メモリセル内のメモリ素子と前記第1の一対のビット線との間に設けられた第1のスイッチの制御端子に、前記第1のページアドレス制御回路からの信号を伝送する第1のワード線と、

前記メモリ素子と前記第2の一対のビット線との間に設けられた第2のスイッチの制御端子に、前記第2のページアドレス制御回路からの信号を伝送する第2のワード線と、

を有することを特徴とするRAM内蔵ドライバ。

【請求項5】 請求項4において、

前記RAMは、前記第1のバスラインを経由した前記静止画データを記憶する第1のRAMと、前記第2のバスラインを経由した前記動画データを記憶する第2のRAMとを有し、

前記表示アドレス制御回路は、前記第1のRAMからの静止画データを表示データとして読み出し制御する第1の表示アドレス制御回路と、前記第2のRAMからの動画データを表示データとして読み出し制御する第2の表示アドレス制御回路とを有し、

前記第1のRAMは、前記第1のカラムアドレス制御回路および前記第1のページアドレス制御回路により書き込みアドレスが制御され、

前記第2のRAMは、前記第2のカラムアドレス制御回路および前記第2のページアドレス制御回路により書き込みアドレスが制御されることを特徴とするRAM内蔵ドライバ。

【請求項6】 請求項3乃至5のいずれかにおいて、

前記第1のカラムアドレス制御回路は、前記MPU系制御回路からの信号に基づいて、前記RAMの読み出しカラムアドレスを指定し、

前記第1のページアドレス制御回路は、前記MPU系制御回路からの信号に基づいて、前記RAMの読み出しページアドレスを指定することを特徴とするRAM内蔵ドライバ。

【請求項7】 複数の第1の電極と複数の第2の電極により駆動される電気 光学素子を有するパネルと、

前記複数の第1の電極を駆動する請求項1乃至6のいずれかに記載のRAM内 蔵ドライバと、

前記複数の第2の電極を走査駆動する走査駆動ドライバと、

を有することを特徴とする表示ユニット。

【請求項8】 請求項7に記載の表示ユニットと、

前記表示ユニットに前記コマンド、前記静止画データおよび前記動画データを 供給するMPUと、

を有することを特徴とする電子機器。

【請求項9】 静止画データおよび動画データに基づいて表示部を表示駆動 して画像を表示させる電子機器であって、

請求項1乃至6のいずれかに記載のRAM内蔵ドライバと、

前記RAM内蔵ドライバのRAMに記憶された画像データに基づいて画像が表示される前記表示部の表示領域に対して、静止画領域を設定する手段と、

前記静止画領域に対応した前記RAMの記憶領域に前記静止画データを書き込む手段と、

前記表示領域に対して動画領域を設定する手段と、

前記動画領域に対応した前記RAMの記憶領域に前記動画データを書き込む手 段と、

を含むことを特徴とする電子機器。

【請求項10】 静止画データおよび動画データに基づいて表示部を表示駆動して画像を表示させる電子機器であって、

請求項1乃至6のいずれかに記載のRAM内蔵ドライバと、

前記RAM内蔵ドライバのRAMに記憶された画像データに基づいて画像が表示される前記表示部の表示領域に対して、静止画領域を設定する手段と、

前記静止画領域に対応した前記RAMの記憶領域に前記静止画データを書き込む手段と、

前記静止画領域に対して任意の動画領域を設定する手段と、

前記動画領域に対応した前記RAMの記憶領域に前記動画データを書き込む手 段と、

を含むことを特徴とする電子機器。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、一画面内に静止画および動画を表示駆動するRAM内蔵ドライバ並びにそれを用いた表示ユニットおよび電子機器に関する。

[0002]

【背景技術および発明が解決しようとする課題】

近年の通信技術、実装技術等の発達により、携帯型の電子機器の表示部に、数字や文字といったキャラクタ文字のみならず、静止画像や動画像などのユーザにとって情報性の高い各種データが表示できるようになった。

# [0003]

このような電子機器に表示されるデータついては、種々のデータ形式が提案されている。例えば携帯電話機を例に挙げれば、MPEG (Moving Picture Experts Group) の規格により圧縮して符号化された画像データを受信または送信する技術が提案されている。

# [0004]

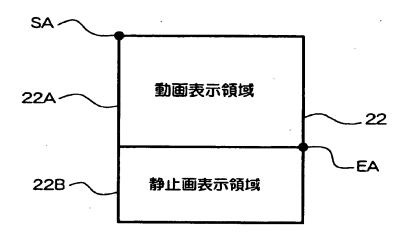

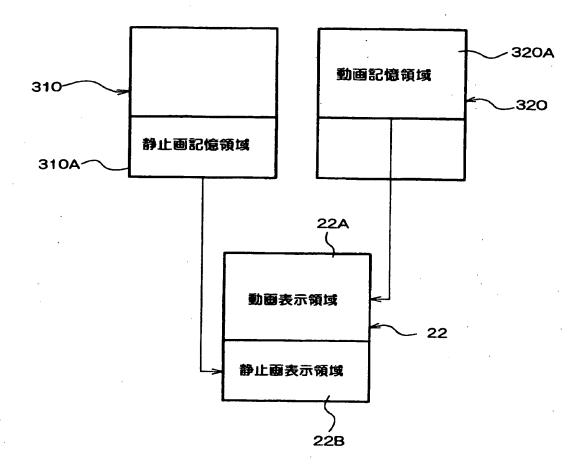

この場合、携帯電話機の表示部には、例えば図3に示す液晶パネル22には、 受信された動画が動画表示領域22Aに表示される。一方、液晶パネル22の静 止画表示領域22Bには、例えばその動画に関する説明、操作情報などの静止画 が表示される。

# [0005]

動画表示領域22Aに動画を表示するためには、液晶ドライバ内のRAMの記憶領域のうち、動画表示領域22Aと対応する動画記憶領域にて、周期的に、しかもほぼリアルタイムに動画データを書き換える必要がある。

#### [0006]

一方、静止画表示領域22Bに表示される静止画は、携帯電話機のキー操作時等に応じて変更され、RAMの記憶領域のうち、静止画表示領域22Bと対応する静止画記憶領域の静止画データを書き換える必要が生じる。

#### [0007]

しかし、RAMの静止画記憶領域にて静止画データを書き換えるには、周期的に動画データが伝送されるバスラインを使用して、一画面の動画データと次の一画面の動画データを伝送する間の隙間を利用するしかない。

#### [0008]

このように、動画データの画面間の限られた時間内で静止画データを伝送することは、動画データおよび静止画データを表示ユニットに供給するMPUの動作時間を拘束し、表示ユニット以外の回路も制御するMPUの動作上の時間的制約

などが大きくなる。

[0009]

そこで、本発明の目的は、RAMに対する動画データの書き換えタイミングとは無関係に、静止画データを書き換えることが可能なRAM内蔵ドライバ並びに それを用いた表示ユニットおよび電子機器を提供することにある。

[0010]

【課題を解決するための手段】

本発明の一態様に係るRAM内蔵ドライバは、静止画データおよび動画データ に基づいて表示部を表示駆動するものである。

[0011]

このRAM内蔵ドライバは、それぞれ静止画データおよび動画データを伝送するための第1および第2のバスラインと、第1および第2のバスラインを介して伝送された静止画データおよび動画データを記憶するRAMと、所与のコマンドに基づいて、RAMに対し、第1又は第2のバスラインを介してそれぞれ別個に伝送された静止画データ又は動画データの書き込み又は読み出し制御する第1の制御回路と、第1の制御回路とは独立して、RAMに記憶された静止画データ又は動画データを表示データとして読み出し制御し、表示部を表示駆動する第2の制御回路とを含むことを特徴とする。

[0012]

本発明の一形態によれば、静止画、動画は、第1、第2のバスラインにより別系統にて伝送される。また、静止画データまたは動画データのRAMへの書き込み制御と、表示部に表示駆動するための表示データのRAMからの読み出し制御とは、それぞれ独立して行われる。

[0013]

このため、動画データをRAMに書き換えながら、同時に静止画データを書き換えることができ、動画データの書き込みの終了を待って、静止画データを書き込む必要がない。しかも、これら静止画データと動画データの書き込み制御に関わらず、表示データによる表示駆動を可能とする。

[0014]

本発明の一形態に係るRAM内蔵ドライバでは、RAMは、第1のバスラインを介して静止画データの書き込みが行われる第1のポートと、第2のバスラインを介して動画データの書き込みが行われる第2のポートと、表示データを読み出すための第3のポートとを有するメモリセルを含むことを特徴とする。

# [0015]

このように、3ポートのメモリセルに対して動画データおよび静止画データを それぞれ別系統で指定し、さらにその他の系統にて蓄積した表示データを読み出 すことができるようにした。これにより、RAMに対する動画データおよび静止 画データの書き込みや、読み出しの制御に必要とされる制約がなくなり、非常に 簡素な処理で表示データのアクセスを行うことができるようになる。

#### [0016]

本発明の一形態に係るRAM内蔵ドライバでは、外部MPUからのコマンド、静止画データおよび動画データに基づいて表示部を表示駆動するRAM内蔵ドライバであって、外部MPUからの静止画データを伝送する第1のバスラインと、外部MPUからの動画データを伝送する第1のバスラインと、静止画データおよび動画データを記憶するRAMと、静止画データを書き込むためのRAMのカラムアドレスを指定する第1のカラムアドレス制御回路と、動画データを書き込むためのRAMのカラムアドレスを指定する第2のカラムアドレス制御回路と、静止画データを書き込むためのRAMのページアドレスを指定する第1のページアドレス制御回路と、動画データを書き込むためのRAMのページアドレス制定する第2のページアドレス制御回路と、外部MPUからのコマンドに基づいて、第1、第2のカラムアドレス制御回路と、外部MPUからのコマンドに基づいて、第1、第2のカラムアドレス制御回路と、外部MPUからのコマンドに基づいて、第1、第2のカラムアドレス制御回路と、RAMに記憶された静止画データおよび動画データを、表示データとして読み出し制御する表示アドレス制御回路と、MPU系制御回路とは独立して、表示アドレス制御回路を制御するドライバ系制御回路とを有することを特徴とする。

#### [0017]

本発明の一形態によれば、静止画、動画データは第1、第2のバスラインにより別系統にて伝送される。また、RAMにデータを書き込むためのカラムおよび

ページアドレスも、静止画と動画とで別系統で指定される。

[0018]

このため、動画データをRAMに書き換えながら、同時に静止画データを書き換えることができ、動画データの書き込みの終了を待って静止画データを書き込む必要がない。

[0019]

本発明の一形態に係るRAM内蔵ドライバでは、RAMのメモリセルに接続された第1の一対のビット線と、RAMのメモリセルに接続された第2の一対のビット線と、第1のカラムアドレス制御回路に制御されて第1の一対のビット線と第1のバスラインとを接続する第1のカラムスイッチと、第2のカラムアドレス制御回路に制御されて第2の一対のビット線と第2のバスラインとを接続する第2のカラムスイッチと、メモリセル内のメモリ素子と第1の一対のビット線との間に設けられた第1のスイッチの制御端子に、第1のページアドレス制御回路からの信号を伝送する第1のワード線と、メモリ素子と第2の一対のビット線との間に設けられた第2のスイッチの制御端子に、第2のページアドレス制御回路からの信号を伝送する第2のワード線とを設けることができる。

[0020]

このように、静止画用と動画用とでポートを異ならせたデュアルポートとしている。すなわち、第1のカラムアドレス制御回路および第1のページアドレス制御回路にて指定されるメモリセルに、第1のビット線対を経由して静止画データを書き込み可能としている。また、第2のカラムアドレス制御回路および第2のページアドレス制御回路にて指定されるメモリセルに、第2のビット線対を経由して動画データを書き込み可能としている。こうして、RAMの記憶領域を拡大せずに、静止画データおよび動画データを任意のセルに書き込むことが可能となる。

[0021]

本発明の一形態に係るRAM内蔵ドライバでは、RAMとして、第1のバスラインを経由した静止画データを記憶する第1のRAMと、第2のバスラインを経由した前記動画データを記憶する第2のRAMとを設けても良い。この場合、表

示アドレス制御回路は、第1のRAMからの静止画データを表示データとして読み出し制御する第1の表示アドレス制御回路と、第2のRAMからの動画データを表示データとして読み出し制御する第2の表示アドレス制御回路とを有する。また、第1のRAMは、第1のカラムアドレス制御回路および第1のページアドレス制御回路により書き込みアドレスが制御され、第2のRAMは、第2のカラムアドレス制御回路および第2のページアドレス制御回路により書き込みアドレスが制御される。

#### [0022]

このように、静止画データ用の第1のRAMと、動画データ用の第2のRAM を有することで記憶領域は拡大されるが、動画データを第2のRAMにて書き換 えながら、同時に静止画データを第1のRAMにて書き換えることができる。

# [0023]

本発明の一形態では、第1のカラムアドレス制御回路は、MPU系制御回路からの信号に基づいて、RAMの読み出しカラムアドレスを指定し、第1のページアドレス制御回路は、MPU系制御回路からの信号に基づいて、RAMの読み出しページアドレスを指定するように構成できる。

#### [0024]

こうすると、一旦RAMに書き込まれたデータを外部MPUに向けて読み出すことが可能となる。例えば、外部MPUがRAMに書き込まれたデータを読み出し、これを反転処理して、再びRAMに書き込むリード・モディファイ・ライト処理を行うことができる。

#### [0025]

本発明の他の形態に係る表示ユニットは、複数の第1の電極と複数の第2の電極により駆動される電気光学素子を有するパネルと、複数の第1の電極を駆動する本発明の一形態に係るRAM内蔵ドライバと、複数の第2の電極を走査駆動する走査駆動ドライバとを有する。

# [0026]

この表示ユニットは、静止画および動画の混合表示を、外部MPUの負担を軽減しながら実現することができる。

# [0027]

本発明のさらに他の態様に係る電子機器は、本発明の他の形態に係る表示ユニットと、表示ユニットにコマンド、静止画データおよび動画データを供給するMPUとを有する。

# [0028]

この電子機器、表示ユニットでの静止画および動画の混合表示に際してMPUの負担が軽減されるので、MPUの稼動効率を高めることができる。

#### [0029]

本発明のさらに他の態様に係る電子機器は、静止画データおよび動画データに基づいて表示部を表示駆動して画像を表示させる電子機器であって、本発明の一形態に係る記載のRAM内蔵ドライバと、RAM内蔵ドライバのRAMに記憶された画像データに基づいて画像が表示される表示部の表示領域に対して、静止画領域を設定する手段と、静止画領域に対応したRAMの記憶領域に静止画データを書き込む手段と、表示領域に対して動画領域を設定する手段と、動画領域に対応したRAMの記憶領域に動画データを書き込む手段とを含む。

# [0030]

本発明によれば、表示部を表示駆動するための表示データを記憶するRAMに対して、静止画データおよび動画データをそれぞれ別個に書き込みすることができるため、従来のように静止画データおよび動画データの混合処理を行ってからRAMに書き込む処理が不要となる。従って、表示データの生成処理が非常に簡素化され、MPU等の処理負荷を大幅に軽減させて、その分高度な画像処理等を行うことができる電子機器を提供することができる。

#### [0031]

本発明のさらに他の態様に係る電子機器は、静止画データおよび動画データに基づいて表示部を表示駆動して画像を表示させる電子機器であって、本発明の一形態に係るRAM内蔵ドライバと、RAM内蔵ドライバのRAMに記憶された画像データに基づいて画像が表示される表示部の表示領域に対して、静止画領域を設定する手段と、静止画領域に対して任意の動画領域を設定する手段と、動画領域に

対応したRAMの記憶領域に動画データを書き込む手段とを含む。

[0032]

本発明によれば、さらに一旦書き込んだ静止画データに上書きするようにして動画データを書き込むことによって、表示部に動画を表示させることができるようになり、表示部において静止画が表示される静止画領域、動画が表示される動画領域の設定状況に関わらず、次々と新しい表示データを書き込むことができ、静止画と動画が混在するような複雑な表示処理の大幅な軽減を図る。

[0033]

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して説明する。

[0034]

<第1の実施の形態>

以下、本発明の第1の実施の形態について、図1~図7を参照して説明する。

[0035]

(電子機器の説明)

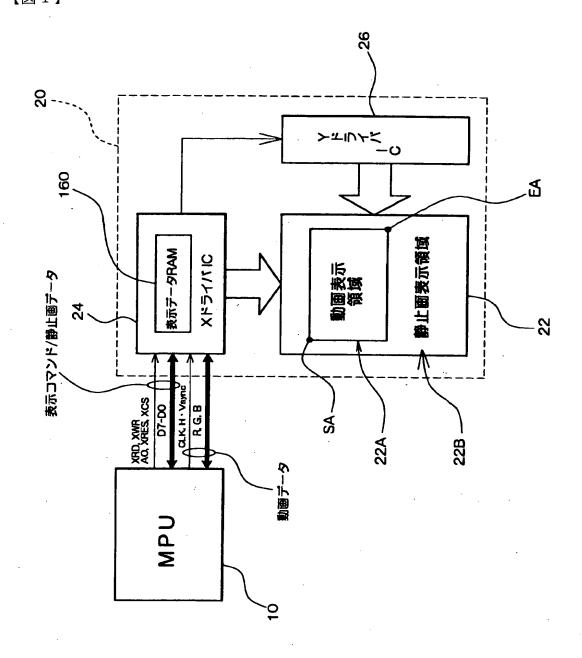

図1は、本発明が適用される電子機器の概略ブロック図である。図1において、この電子機器は、MPU(マイクロプロセッサユニット)10と、表示ユニット20とから構成される。表示ユニット20は、電気光学素子を有するマトリクスパネル例えばカラー液晶パネル22と、この液晶パネル22を駆動するRAM内蔵のXドライバIC24と、走査用のYドライバIC26とを有する。

[0036]

マトリクスパネル22は、電圧印加によって光学特性が変化する液晶その他の電気光学素子を用いたものであればよい。液晶パネル22としては、例えば単純マトリクスパネルで構成でき、この場合、複数のセグメント電極(第1の電極)が形成された第1基板と、コモン電極(第2の電極)が形成された第2基板との間に、液晶が封入される。液晶パネル22は薄膜トランジスタ(TFT)、薄膜ダイオード(TFD)等の三端子素子、二端子素子を用いたアクティブマトリクスパネルであっても良い。これらのアクティブマトリクスパネルも、RAM内蔵XドライバIC24により駆動される複数の信号電極(第1の電極)と、Yドラ

イバIC26により走査駆動される複数の走査電極(第2の電極)を有する。

[0037]

液晶パネル22には静止画と動画とを同時に表示可能である。この場合、図1に示すように、MPU10によって供給された動画データの画像サイズによって 定められる動画表示領域22Aと、それ以外の静止画表示領域(テキストデータ 表示領域)22Bの各領域が液晶パネル22に設定される。

[0038]

MPU10から表示ユニット20には、図1に示すように、大別して表示コマンド/静止画データと、動画データとが供給される。表示コマンドとして代表的なものに、コマンド/データの区別を示す信号A0、反転リセット信号XRES、反転チップセレクト信号XCS、反転リード信号XRDおよび反転ライト信号XWR等がある。データD7~D0は8ビットのコマンドデータ(静止画および動画用アドレスデータを含む)または静止画データであり、コマンド/データ識別信号A0の論理によって区別されている。動画データは例えば各6ビットのR、G、B信号であり、クロック信号CLK、水平・垂直同期信号H・Vsync等も供給される。

[0039]

このように、本実施の形態では、表示コマンド/静止画データのためのバスと 、動画データのためのバスとが分離されている。

[0040]

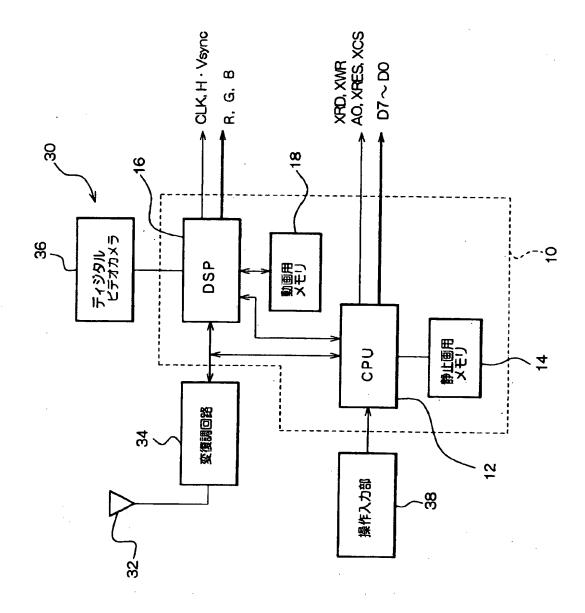

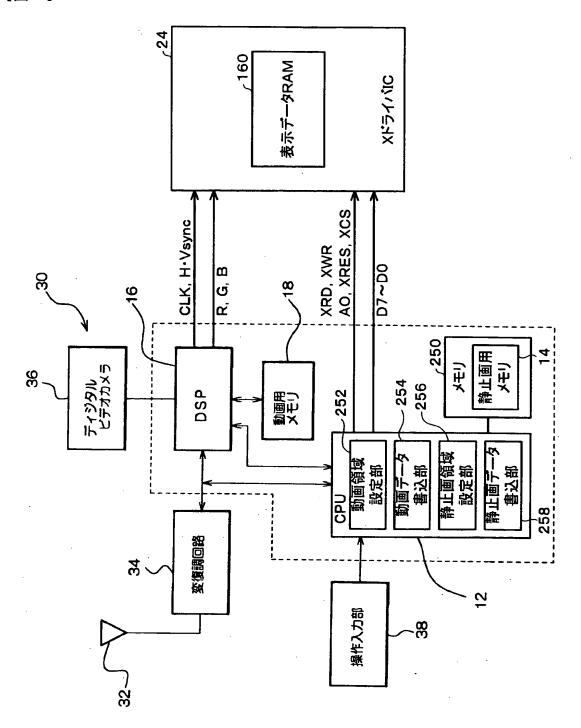

図2は、図1のMPU10および表示ユニット20を携帯電話機30に搭載した例を示している。図2に示すMPU10は、携帯電話機30の制御を司るCPU12を有し、このCPU12には静止画用メモリ14、DSP(ディジタル・シグナル・プロセッサ)16が接続されている。また、DSP16には動画用メモリ18が接続されている。

[0041]

この携帯電話機30には、アンテナ32を介して受信された信号を復調し、あるいはアンテナ32を介して送信される信号を変調する変復調回路34が設けられている。そして、アンテナ32からは、例えばMPEG (Moving Picture Exp

erts Group) のレイヤーIVの規格にて符号化された動画データを送受信可能となっている。

# [0042]

この携帯電話機30には、例えばディジタルビデオカメラ36を設けることもできる。このディジタルビデオカメラ36を介して動画データを取り込むことができる。携帯電話機30でのデータ送受信、ディジタルビデオカメラ36での撮影などに必要な操作情報は、操作入力部38を介して入力される。

# [0043]

MPU10に設けられたCPU12は、液晶パネル22の動画表示領域22Aに動画を表示する際には、その動画のサイズを動画情報から決定する。すなわち、図1に示す動画のスタートアドレスSA及びエンドアドレスEAを決定する。なお、図3に示すように動画表示領域22Aと静止画表示領域22Bとを例えば上下でライン分割しても良く、この場合も同様にスタートアドレスSA、エンドアドレスEAが動画のサイズから決定される。

#### [0044]

この動画表示領域22Aに表示される動画は、本実施の形態ではアンテナ32またはディジタルビデオカメラ36から供給される。アンテナ32から入される信号は、変復調回路34を介して復調されてDSP16にて信号処理される。このDSP16は動画処理用メモリ18と接続され、アンテナ32、変復調回路34を介して入力される圧縮データを伸張し、またMPEGのレイヤーIVの規格にて符号化されているデータについてはデコードする。変復調回路34、アンテナ32を介して送信されるデータはDSP16にて圧縮され、MPEGのレイヤーIVの規格にて符号化して送信する場合にはエンコードされる。このようにDSP16は、MPEGの例えばレイヤーIVのデコーダ、エンコーダとしての機能を有することができる。

# [0045]

このDSP16にはディジタルビデオカメラ36からの信号も入力され、アンテナ32またはディジタルビデオカメラ36より入力された信号は、DSP16にてRGB信号に処理されて表示ユニット20に供給される。

[0046]

CPU12は、操作入力部38からの情報等に基づき、必要により静止画用メモリ14を用いて、液晶パネル22に表示される静止画の表示に必要なコマンド、静止画データを表示ユニット20に出力する。

[0047]

例えば、動画はインターネットを経由して配信された映画情報であり、その劇場チケットを予約するための情報が静止画として表示され、操作入力部38からの情報に基づいてチケット予約が実施される。このため、CPU12はさらに、変復調回路34、アンテナ32を介して静止画情報(例えば予約情報)を送出制御する。またCPU12は、必要により、ディジタルビデオカメラ36にて撮影された動画情報を、変復調回路34、アンテナ32を介して送出制御することができる。

[0048]

(XドライバICの説明)

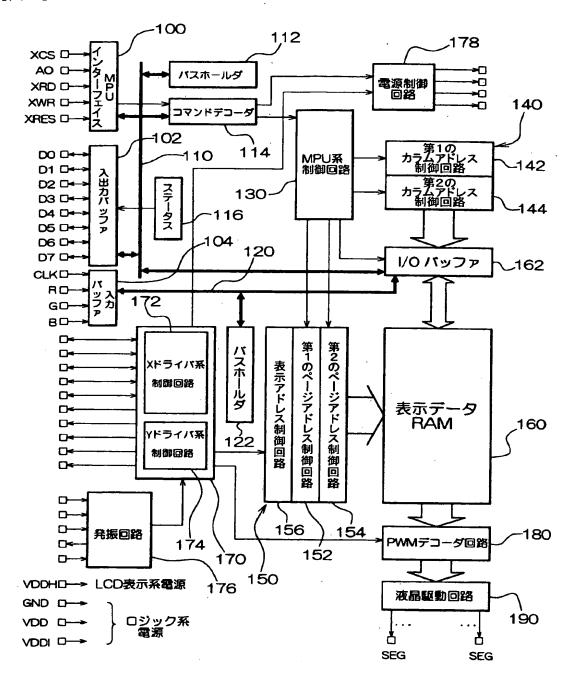

図4は図1に示すRAM内蔵XドライバIC24のブロック図である。図4に示すRAM内蔵XドライバIC24の入出力回路として、MPUインターフェース100と入出力バッファ102、入力バッファ104が設けられている。

[0049]

MPUインターフェース100には、反転チップセレクト信号XCS、コマンド/データの識別信号A0、反転リード信号XRD、反転ライト信号XWR、反転リセット信号XRESなどが入力される。

[0050]

入出力バッファ102には、例えば8ビットのコマンドまたは静止画データD7~D0が入力される。なお、図4では信号D7~D0はパラレルで入出力される例を示しているが、XドライバIC24内の表示データRAM160からMPU10にデータを読み出す必要がない場合には、先頭ビットを識別信号A0とし、それに続く信号D7~D0をシリアルで入出力してもよい。こうすると、MPU10及びXドライバIC24の端子数を減らすことができる。

[0051]

入力バッファ104には、例えば各6ビットのR, G, B信号からなる動画データと、クロック信号CLKとが入力される。各6ビットのR, G, B信号は、クロック信号CLKに同期してパラレルで入出力される。

[0052]

XドライバIC24には、MPUインターフェース100及び入出力バッファ 102に接続された第1のバスライン110と、入力バッファ104に接続され た第2のバスライン120とが設けられている。

[0053]

第1のバスライン110にはバスホールダ112とコマンドデコーダ114とが接続され、第2のバスライン120にはバスホールダ122が接続されている。なお、入出力バッファ102にはステータス設定回路116が接続され、XドライバIC24の動作状態がMPU10に出力されるようになっている。この動作状態とは、例えば表示がオン状態であるか否か、画面内の所与のスクロール領域のスクロールモードといったXドライバIC24で設定されている内部状態であって、MPU10から入力された所与のコマンドがコマンドデコーダ114でデコードされた結果、出力されるようになっている。

[0054]

第1,第2のバスライン110,120は共に、表示データRAM160のI /Oバッファ162に接続され、表示データRAM160に対してリード、ライトされる静止画データ及び動画データが伝送される。

[0055]

XドライバIC24には、上述した表示データRAM160、I/Oバッファ 162の他に、MPU系制御回路130、カラムアドレス制御回路140、ペー ジアドレス制御回路150、ドライバ系制御回路170、PMWデコード回路1 80及び液晶駆動回路190などが設けられている。

[0056]

MPU系制御回路130は、コマンドデコーダ114を介して入力されるMPU10のコマンドに基づいて、表示データRAM160に対するリード、ライト動作を制御する。このMPU系制御回路130により制御されるカラムアドレス

1 5

制御回路140及びページアドレス制御回路150が設けられている。本実施の 形態では、カラムアドレス制御回路140は、静止画データの書き込みカラムア ドレスと静止画及び動画データの読み出しカラムアドレスを指定する第1のカラ ムアドレス制御回路142と、動画データの書き込みカラムアドレスを指定する 第2のカラムアドレス制御回路144とを有する。ページアドレス制御回路15 0は、静止画データの書き込みページアドレスと静止画及び動画データの読み出 しページアドレスとを指定する第1のページアドレス制御回路152と、動画デ ータの書き込みページアドレスを指定する第2のページアドレス制御回路154 とを有する。なお、図4では図示していないが、MPU10からの垂直、水平同 期信号H・VsyncがMPU系制御回路130に入力される。水平同期信号H syncは、動画データの書き込みの際のノイズ等の誤書き込みによる表示ずれ 等を極力抑えるために、第2のカラム・ページアドレス制御回路144,154 内に設けられたカウンタのセット、リセットに用いられる。さらに、水平・垂直 同期信号H・Vsyncは、カラムアドレス、ページアドレスをスタートアドレ スSAに戻すために用いられる。また、ページアドレス制御回路150は、ドラ イバ系制御回路170により制御されて1ライン毎に表示アドレスを指定する表 示アドレス制御回路156を含んでいる。

#### [0057]

ドライバ系制御回路170は、Xドライバ系制御回路172及びYドライバ系制御回路174を含む。このドライバ系制御回路170は、発振回路176からの発振出力に基づいて階調制御パルスGCP、極性反転信号FR、ラッチパルスLPなどを発生し、MPU系制御回路130とは独立して、表示アドレス制御回路156、PWMデコード回路180、電源制御回路178およびYドライIC26を制御する。

#### [0058]

PWMデコード回路180は、表示データRAM160より1ライン毎に読み出されるデータをラッチして、極性反転周期に従って階調値に応じたパルス幅の信号を出力する。液晶駆動回路190は、PWMデコード回路180からの信号を、LCD表示系の電圧に応じた電圧にシフトさせ、図1に示す液晶パネル20

のセグメント電極SEGに供給する。

[0059]

(表示データRAMおよびその周辺回路の説明)

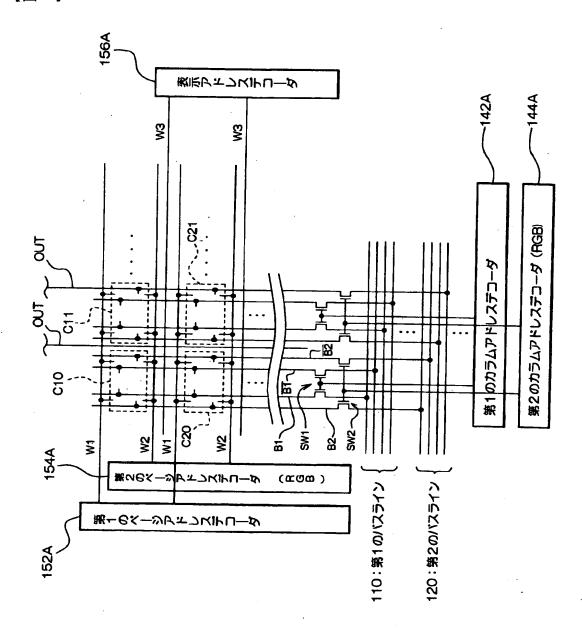

図5は表示データRAM160およびその周辺回路の概略回路図である。図5には、第1,第2のカラムアドレス制御回路142,144、第1,第2のページアドレス制御回路152,154および表示アドレス制御回路156のそれぞれの最終段に設けられた第1,第2のカラムアドレスデコーダ142A,144A、第1,第2のページアドレスデコーダ152A,154Aおよび表示アドレスデコーダ156Aが示されている。

[0060]

図5にはさらに、第1,第2行目のメモリセルC10,C11…、C20,C21…が示されている。そして、図5に示す各メモリセルには、第1~第3のワード線W1~W3と、第1のビット線対B1,/B1と、第2のビット線対B2,/B2とが接続されている。

[0061]

第1のカラムアドレスデコーダ142Aは、第1のビット線対B1、/B1に接続された第1のカラムスイッチSW1をオン、オフさせる信号を出力する。第2のカラムアドレスデコーダ144Aは、第2のビット線対B2、/B2に接続された第2のカラムスイッチSW2をオン、オフさせる信号を出力する。第1のページアドレスデコーダ152Aは第1のワード線W1を、第2のページアドレスデコーダ156Aは第3のワードラインW3を、それぞれをアクティブとする信号を供給する。

[0062]

従来技術と比較すると、本実施の形態では、第2のワード線W2と、第2のビット線対B2, /B2と、第2のカラムスイッチSW2と、第2のカラムアドレスデコーダ144Aと、第2のページアドレスデコーダ154Aとが新たに設けられている。

[0063]

第2のカラムおよびページアドレスデコーダ144A, 154Aは、動画デー

タ(R, G, B)を書き込むためのカラムおよびページアドレスを指定する場合にのみ用いられ、このアドレス指定により第2のバスライン120、第2のカラムスイッチSW2を介して、動画データ(R, G, B)がメモリセルに書き込まれる。

#### [0064]

第1のカラムおよびページアドレスデコーダ142A, 152Aは、静止画データを書き込む時と、静止画および動画データを読み出す時に、カラムおよびページアドレスを指定する。このアドレス指定により第1のバスライン120、第1のカラムスイッチSW1を介して、表示データRAM160に対してデータがリード・ライトされる。

# [0065]

表示アドレスデコーダ156Aは、第3のワード線W3を順次1本ずつアクティブにすることで、1ライン上の全メモリセルのデータを表示データ出力線OUTに読み出すものである。この読み出しデータが図4に示すPWMデコーダ回路180に供給されて液晶駆動に供される。

#### [0066]

#### (メモリセルの構成について)

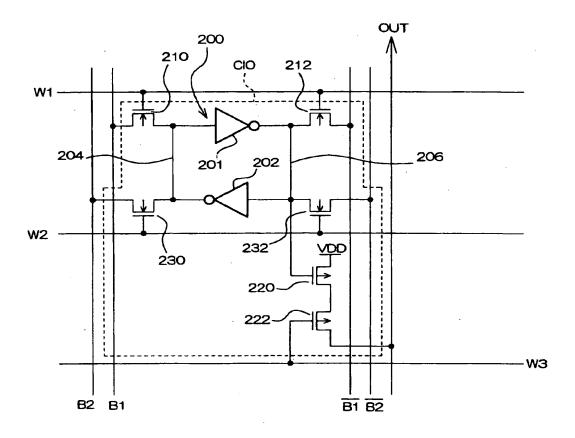

図6は表示データRAM160内のメモリセルC10を示す回路図である。メモリセルC10は、他のメモリセルと同一の構成を有する。このメモリセルC10は、2つのCMOSインバータ210,202にて構成されるメモリ素子200を有する。2つのMOSインバータ201,202は、その入出力同士を互いに接続する第1,第2の配線204,206を有する。第1配線204とビット線B1との間には第1のN型MOSトランジスタ210(第1のスイッチ)が接続され、そのゲートは第1のワード線W1に接続されている。同様に、第2配線206とビット線/B1との間には第2のN型MOSトランジスタ212(第1のスイッチ)が接続され、そのゲートは第1のワード線W1に接続されている。

#### [0067]

以上の構成により、第1のページアドレスデコーダ152Aからのアクティブ 信号により第1のワード線W1がHとなると、第1,第2のN型トランジスタ2 10,212がオンされる。これにより、メモリセルC10は第1の一対のビット線B1,/B1と接続される。このとき、第1のカラムアドレスデコーダ14 2Aからアクティブ信号により第1のカラムスイッチSW1がオンしていると、 メモリセルC10に対するデータのリード・ライトが可能となる。

# [0068]

また、電源供給線VDDと表示データ出力線OUTとの間には第1,第2のP型MOSトランジスタ220,222が接続されている。第1のP型MOSトランジスタ220のゲートは第2の配線206に接続され、第2のP型MOSトランジスタ222のゲートは第3のワード線W3に接続されている。

# [0069]

メモリセルC10のデータを表示データ出力線OUTに読み出す前に、この表示データ出力線OUTはLにプリチャージされている。このプリチャージ動作後に第3のワード線W3をLとして第2のP型MOSトランジスタ222をオンさせた状態で、表示データ出力線OUTのデータがPWMデコーダ回路180にてラッチされる。このとき、第2の配線206の電位がH(第1の配線204の電位がL)であれば表示データ出力線OUTはLのままであり、第2の配線206の電位がL(第1の配線204の電位がH)であれば表示データ出力線OUTはHとなる。このようにして、表示データRAM160からの表示データの読み出しを1ライン同時に行うことができる。

#### [0070]

本実施の形態ではさらに、第2のワード線W2と第2のビット線対B2, /B2とが設けられている。このため、第1配線204とビット線B2との間には第3のN型MOSトランジスタ230(第2のスイッチ)が接続され、そのゲートは第2のワード線W2に接続されている。同様に、第2配線206とビット線/B2との間には第4のN型MOSトランジスタ232(第2のスイッチ)が接続され、そのゲートは第2のワード線W2に接続されている。

#### [0071]

以上の構成により、第2のページアドレスデコーダ154Aからのアクティブ 信号により第2のワード線W2がHとなると、第3,第4のN型トランジスタ2 30,232がオンされ、メモリセルC10は第2の一対のビット線B2,/B 2と接続される。このとき、第2のカラムアドレスデコーダ144Aからアクティブ信号により第2のカラムスイッチSW2がオンしていると、メモリセルC1 0に対する動画データのライトが可能となる。

[0072]

(表示データRAMに対する静止画、動画の書き込みについて)

MPU10は、図1または図3に示す動画表示領域22AのスタートおよびエンドアドレスSA、EAと対応する表示データRAM160のページアドレスおよびカラムアドレスを、動画情報から予め知得している。このためMPU10は、表示データRAM160のエリアのうち動画表示領域22Aと対応するエリアのカラムアドレスおよびページアドレスを、所定の書き込み周波数に従って繰り返し指定することが可能となる。この動画表示領域22Aと対応するエリアのカラムアドレスおよびページアドレスは、XドライバIC24の入出力バッファ102、MPU系制御回路130を経由して、第2のカラムアドレス制御回路144および第2のページアドレス制御回路154に入力される。最終的に、図5に示す第2のカラムアドレスデコーダ154Aを介して、表示データRAM160のカラムおよびページアドレスが指定される。動画データについて、入力バッファ104および第2のバスライン120を経由させることで、静止画データのバスライン110とは異なる経路にてリアルタイムで伝送することができ、それにより動画データがリアルタイムで書き換えられることになる。

[0073]

一方MPU10は、表示データRAM160のエリアのうち静止画表示領域22Aと対応するエリアのカラムアドレスおよびページアドレスを指定して、操作入力部38からの情報入力があった時などの静止画データに変更が生じた時にのみ、所定の書き込み周波数にてデータ書き換えを実施する。

[0074]

このように、本実施の形態では、静止画と動画とを表示データRAM160に 書き込むにあたって、アドレス指定およびデータ伝送をそれぞれ別ルートにて実 施し、メモリセルはそれらのいずれのデータも書き込めるように構成されている 。従って、静止画と動画とを同時にページ単位で異なるメモリセルに書き込むこ とが可能となり、どちらか一方のデータ書き込みを停止する必要はない。

[0075]

また、メモリセルは静止画および動画のいずれのデータも書き込めるように構成されているので、動画表示領域22Aを任意に変更することが可能となる。

[0076]

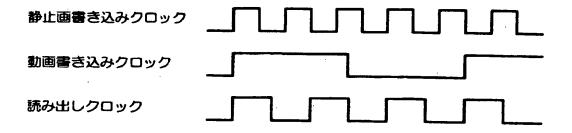

ここで、液晶パネル20の動画表示領域22Aに動画を表示するに際しては、例えば60Hzすなわち1秒間に60フレームを表示できる図7に示す読み出しクロックに従って、表示データRAM160から表示データが読み出される。

[0077]

一方、静止画データは、液晶表示のための駆動周波数より高い例えば90Hz すなわち1秒間に90フレームを表示できる静止画書き込みクロックに従って、 表示データRAM160に表示データが書き込まれる。このように、表示読み出 しレートより高い書き込みレートにて静止画の書き換えを実施しているため、操 作入力部38での操作に応じたスクロール表示等に追従した表示が可能となる。

[0078]

これに対して動画データについては、人間の網膜の残像現象を利用するものであるので、携帯電話機などのように精密な動画表示が求められない場合には、動画のフレーム数を低く(表示に合わせて60フレーム全部を書き換える必要はない)しても支障はない。本実施の形態では、例えば20Hzすなわち1秒間に20フレームの動画データを書き込むことができる周波数で書き込みを行うこともできるし、60フレームの周波数にて20/60=1/3のデータをMPU10からXドライバIC24に送出するだけでもよい。RAMを内蔵していないXドライバICを使用する場合には60フレーム分のデータを常に書き換える必要があるが、このように動画の書き込み周波数を低く(書き込みレートを低く)し、または書き換えられるデータ量を減少することで、静止画とは異なり表示データRAM160の内容を常時書き換える必要がある動画データの書き込み回数が少なくなり、その分メモリセルにて消費される電力を少なくすることができる。

[0079]

(本実施形態に係る電子機器の具体例)

次に、上述した第1の実施の形態におけるXドライバIC24を備える電子機器について、具体的に説明する。

[0080]

図8は、本発明の第1の実施の形態に係るXドライバIC24を備える電子機器としての携帯電話機の一例の構成要部を示すブロック図である。なお、図8において図2と同一機能を有する回路については、図2と同一の符号を用いその詳細な説明を省略する。

[0081]

第1の実施の形態におけるCPU12には、メモリ250が接続されている。メモリ250は、CPU12によって実行されるプログラムが記憶されたプログラムメモリと、静止画用メモリ14とを含む。CPU12は、このプログラムメモリに記憶されたプログラムにしたがって、液晶パネル22に静止画または動画を表示させるためにXドライバIC24に対し、静止画データまたは動画データを伝送させる。すなわち、CPU12は、液晶パネル22に静止画を表示させるための静止画データをXドライバIC24に対して伝送すると共に、液晶パネル22に動画を表示させるための動画データの生成と伝送とをDPS16に対して指示を行う。従って、静止画データと動画データとは、別系統でXドライバIC24に対し伝送されるようになっている。

[0082]

このため、CPU12は、少なくとも動画領域設定部252、動画データ書込部254、静止画領域設定部256、静止画データ書込部258を含む。

[0083]

動画領域設定部252は、XドライバIC24の表示データRAM160に記憶される表示データに基づいて、液晶パネル22に画像が表示される表示領域の任意の位置にスタートアドレスSAとエンドアドレスEAによって特定される動画領域を設定する。この動画領域は、例えば液晶パネル22の表示領域のマトリックス状の各画素をそれぞれアドレスで定義づけた場合、スタートアドレスSA

とエンドアドレスEAとを結ぶ対角線によって特定される矩形領域とすることができる。

#### [0084]

動画データ書込部254は、DSP16に対し、動画領域設定部252によって設定された動画領域に動画データの書き込み指示を行う。DSP16は、CPU12の動画領域設定部252によって設定された動画領域に動画情報が表示されるように生成した動画用メモリ18に記憶された動画データをXドライバIC24に伝送し、設定された動画領域に対応した表示データRAM160の記憶領域に書き込む。

#### [0085]

静止画領域設定部256は、XドライバIC24の表示データRAM160に記憶される表示データに基づいて、液晶パネル22に画像が表示される表示領域の任意の位置に、静止画領域を設定する。この静止画領域は、動画領域と同様に、別のスタートアドレスSA、とエンドアドレスEA、によって特定される領域である。この静止画領域についても、例えば液晶パネル22の表示領域のマトリックス状に配置された各画素をそれぞれアドレスで定義づけた場合、スタートアドレスSA、とエンドアドレスEA、とを結ぶ対角線によって特定される矩形領域とすることができる。

#### [0086]

静止画データ書込部258は、静止画領域設定部256によって設定された静止画領域に静止画データを書き込む。より具体的には、CPU12は、静止画領域設定部256によって設定された静止画領域にテキストなどの静止画情報が表示されるように生成した静止画用メモリ14に記憶された静止画データをXドライバIC24に伝送し、設定された静止画領域に対応した表示データRAM160の記憶領域に書き込む。

# [0087]

なお、このようなCPU12の機能は、その全てをハードウェアにより実現してもよいし、その全てをプログラムにより実現してもよい。或いは、ハードウェアとプログラムの両方により実現してもよい。

#### [0088]

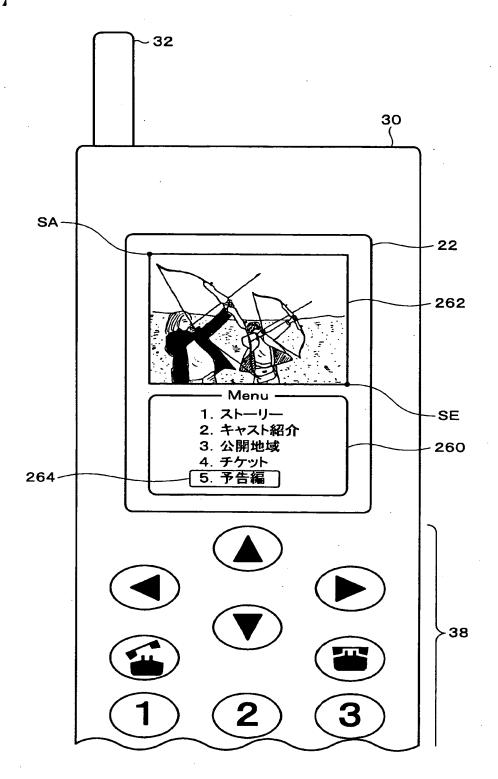

図9は、このようなCPU12の機能によって実現された電子機器としての携帯電話機の表示部の一例を示したものである。

# [0089]

ここでは、例えば携帯電話機30のユーザがインターネット上のコンテンツサーバにアクセスし、映画情報を提供するコンテンツを表示させた場合を示している。

#### [0090]

ユーザは、操作入力部38としてのキーを操作し、インターネットを介して所 与のコンテンツサーバにアクセスすることによって、コンテンツデータを受信す る。このコンテンツデータは、動画および静止画が混在し、それぞれ動画情報お よび静止画情報に画像サイズが含まれているものとする。動画情報および静止画 情報に画像サイズに関する情報が含まれていないときは、液晶パネル22の表示 領域全てを表示すべき画像サイズとする。

# [0091]

第1の実施形態における携帯電話機30は、受信したコンテンツデータに含まれる動画情報または静止画情報から画像サイズを検出し、それぞれ動画表示領域または静止画(またはテキスト)表示領域を設定するようになっている。ここでは、図9に示すように、携帯電話機30の表示部である液晶パネル22の表示領域の下側部分に静止画表示領域260、上側部分に動画表示領域260が設定されている場合を示している。

#### [0092]

静止画表示領域260には、アクセスしたコンテンツサーバによって提供される各種サービスを選択するためのメニュー画面が表示される。ユーザは、操作入力部38のキー操作によってカーソル264を移動させて、所望の項目を選択することによって、選択した項目に対応するサービスの提供を受ける。

#### [0093]

第1の実施の形態における電子機器では、静止画領域260に表示されたメニュー画面の各項目に対応した画像を、液晶パネル22の所与の位置に表示させる

ことができるようになっている。

[0094]

例えば、「1. ストーリー」を選択した場合、テキスト文字からなる映画のストーリー情報をコンテンツサーバから取得し、液晶パネル22の所与の位置に表示させる。また、例えば「4. チケット」を選択した場合、その映画の劇場チケットを予約するための情報が液晶パネル22の所与の静止画領域に静止画として表示され、操作入力部38からの情報に基づいてチケット予約が実施されるようになっている。この静止画表示領域は、表示される静止画情報に応じて、その大きさ、表示領域が異なる。さらにまた、例えば「5. 予告編」を選択した場合、コンテンツサーバから映画の予告編情報を動画データとして取得し、動画表示領域262に動画を表示させる。この動画表示領域262は、表示させる動画情報に応じて、その大きさ、表示領域が異なる。

[0095]

さらに、第1の実施の形態における電子機器では、ユーザがキー操作によりメニュー画面で選択を行わない場合に、コンテンツサーバから次々と宣伝広告を目的とした動画が液晶パネル22の所与の位置に表示されるようになり、新たな宣伝広告媒体の1つとなり得る。

[0096]

このような電子機器は、CPU12によって次のような処理を行うプログラムが実行されることで実現される。

[0097]

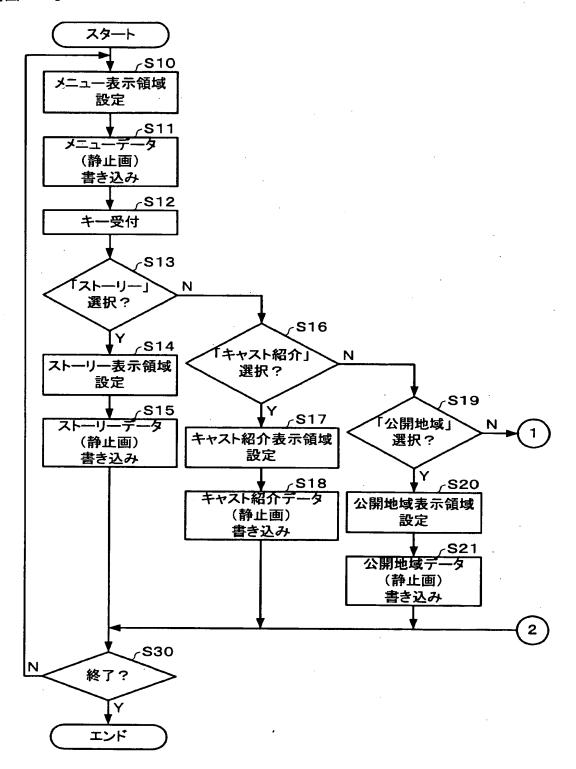

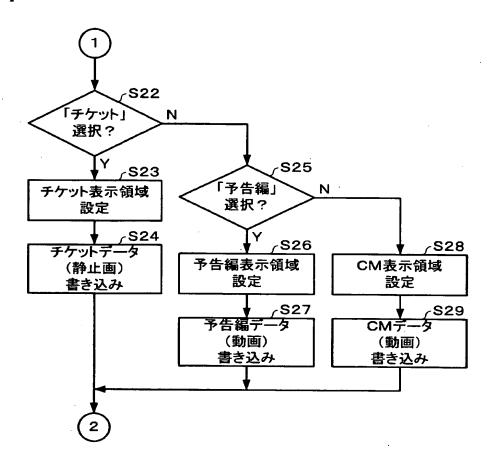

図10および図11は、上述した静止画と動画が混在したコンテンツデータを 表示させるプログラムの処理内容の一例である。

[0098]

CPU12は、インターネットを介してコンテンツデータに含まれるメニュー情報を取得すると、静止画領域設定部256によりメニュー画面を表示するための静止画情報に基づいて、液晶パネル22の表示領域内でメニュー表示領域を設定する(ステップS10)。

[0099]

続いて、静止画設定領域258により、メニュー画面を表示させるためのメニューデータ(静止画情報)を、設定したメニュー表示領域に対応したXドライバIC24の表示データRAM160の記憶領域に書き込む(ステップS11)。 すなわち、XドライバIC24に伝送して、所与のコマンドにより表示データRAM160に書き込み制御を行う。

[0100]

その後、ユーザによる操作入力部38を介したキー入力を受け付ける(ステップS12)。

[0101]

その結果、ユーザの操作入力部38を介したキー入力により、メニュー画面の選択項目のうち「1.ストーリー」が選択されたとき(ステップS13:Y)、選択項目「1」が選択された旨をコンテンツサーバに通知して、これに対応したコンテンツデータ(ストーリー情報)を取得する。このコンテンツデータ(ストーリー情報)は、例えば選択されている映画のストーリーの内容を表示するための静止画情報である。

[0102]

静止画領域設定部256は、取得したコンテンツデータ(ストーリー情報)に含まれ、ストーリーを表示するテキスト画面を表示するための静止画情報に基づいて、液晶パネル22の表示領域内でストーリー表示領域を設定する(ステップ S14)。

[0103]

続いて、静止画データ書込部258により、選択された映画のストーリー内容を表示させるためのストーリー情報(静止画情報)を、設定したストーリー表示領域に対応したXドライバIC24の表示データRAM160の記憶領域に書き込む(ステップS15)。すなわち、XドライバIC24に伝送して、所与のコマンドにより表示データRAM160に書き込み制御を行う。

[0104]

一方、ステップS13で、ユーザの操作入力部38を介したキー入力により、 メニュー画面の選択項目のうち「2. キャスト紹介」が選択されたとき(ステッ

# [0105]

静止画領域設定部256は、取得したコンテンツデータ(キャスト紹介情報) に含まれ、キャスト紹介を表示するテキスト画面を表示するための静止画情報に 基づいて、液晶パネル22の表示領域内でキャスト紹介表示領域を設定する(ス テップS17)。

# [0106]

続いて、静止画データ書込部258により、選択された映画のキャスト紹介内容を表示させるためのキャスト紹介情報(静止画情報)を、設定したキャスト紹介表示領域に対応したXドライバIC24の表示データRAM160の記憶領域に書き込む(ステップS18)。すなわち、XドライバIC24に伝送して、所与のコマンドにより表示データRAM160に書き込み制御を行う。

#### [0107]

また、ステップS16で、ユーザの操作入力部38を介したキー入力により、 メニュー画面の選択項目のうち「3.公開地域」が選択されたとき(ステップS 16:N、ステップS19:Y)、選択項目「3」が選択された旨をコンテンツ サーバに通知して、これに対応したコンテンツデータ(公開地域情報)を取得す る。このコンテンツデータ(公開地域情報)は、例えば選択されている映画が公 開される地域や劇場などの公開場所を特定する内容を表示するための静止画情報 である。

# [0108]

静止画領域設定部256は、取得したコンテンツデータ(公開地域情報)に含まれ、公開地域を表示するテキスト画面を表示するための静止画情報に基づいて、液晶パネル22の表示領域内で公開地域表示領域を設定する(ステップS20)。

#### [0109]

続いて、静止画データ書込部258により、選択された映画の公開地域を表示させるための公開地域情報(静止画情報)を、設定した公開地域表示領域に対応したXドライバIC24の表示データRAM160の記憶領域に書き込む(ステップS21)。すなわち、XドライバIC24に伝送して、所与のコマンドにより表示データRAM160に書き込み制御を行う。

# [0110]

さらに、ステップS19で、ユーザの操作入力部38を介したキー入力により、メニュー画面の選択項目のうち「4. チケット」が選択されたとき(ステップS19:N、ステップS22:Y)、選択項目「4」が選択された旨をコンテンツサーバに通知して、これに対応したコンテンツデータ(チケット情報)を取得する。このコンテンツデータ(チケット情報)は、例えば選択されている映画の劇場チケットを予約するための案内を表示するための静止画情報である。

# [0111]

静止画領域設定部256は、取得したコンテンツデータ(チケット情報)に含まれ、チケット予約案内を表示するテキスト画面を表示するための静止画情報に基づいて、液晶パネル22の表示領域内でチケット表示領域を設定する(ステップS23)。

#### [0112]

続いて、静止画データ書込部258により、選択された映画の劇場チケットの予約案内を表示させるためのチケット情報(静止画情報)を、設定したチケット表示領域に対応したXドライバIC24の表示データRAM160の記憶領域に書き込む(ステップS24)。すなわち、XドライバIC24に伝送して、所与のコマンドにより表示データRAM160に書き込み制御を行う。

#### [0113]

ここで、ユーザが、表示されたチケット予約案内にしたがってチケット予約を 行った場合、実際にはチケット予約に伴うチケット手配や決済を含むチケット予 約処理が行われる。

#### [0114]

ステップS22で、ユーザの操作入力部38を介したキー入力により、メニュ

- 画面の選択項目のうち「5. 予告編」が選択されたとき(ステップS22:N、ステップS25:Y)、選択項目「5」が選択された旨をコンテンツサーバに通知して、これに対応したコンテンツデータ(予告編情報)を取得する。このコンテンツデータ(予告編情報)は、例えば選択されている映画の予告編の内容を表示するための動画情報である。

# [0115]

動画領域設定部252は、取得したコンテンツデータ(予告編情報)に含まれ、予告編の内容を表示するための動画情報に基づいて、液晶パネル22の表示領域内で予告編表示領域を設定する(ステップS26)。

# [0116]

続いて、動画データ書込部254により、選択された映画の予告編を表示させるための予告編情報(動画情報)を、設定した予告編表示領域に対応したXドライバIC24の表示データRAM160の記憶領域に書き込む(ステップS27)。すなわち、DSP16に対して、書き込むべき動画データのXドライバIC24に対する伝送を指示して、表示データRAM160に書き込みを行わせる。

#### [0117]

ステップS25でも、ユーザの操作入力部38を介したキー入力により、メニュー画面の選択項目のうち「5.予告編」が選択されないとき(ステップS25:N)、インターネットを介してコンテンツサーバから配信される宣伝広告を目的とした動画情報の表示処理を行う。

#### [0118]

すなわち、取得したコンテンツデータに含まれる宣伝広告のための動画情報から、動画領域設定部252により、液晶パネル22の表示領域内でCM表示領域を設定する(ステップS28)。このCM表示領域は、取得したコンテンツデータに含まれる宣伝広告のための動画情報によって指定されている領域であっても良いし、ユーザによって指定された領域であっても良い。

#### [0119]

続いて、動画データ書込部254により、取得した宣伝広告のためのCM情報 (動画情報)を、設定したCM表示領域に対応したXドライバIC24の表示デ ータRAM160の記憶領域に書き込む(ステップS29)。すなわち、DSP 16に対して、書き込むべき動画データのXドライバIC24に対する伝送を指 示して、表示データRAM160に書き込みを行わせる。

# [0120]

ステップS15、ステップS18、ステップS21、ステップS24、ステップS27或いはステップS29で、静止画データまたは動画データが表示データRAM160に書き込まれると、XドライバIC24などで液晶パネル22を含む表示部を表示駆動して、静止画および動画が混在したコンテンツが表示される

その後、このコンテンツサービスを終了するときは(ステップS30:Y)、一連の表示処理を終了する(エンド)。コンテンツサービスを終了しないとき(ステップS30:N)、再びステップS10に戻ってメニュー表示を行う。

# [0121]

# <第2の実施の形態>

本発明の第1の実施の形態に係るXドライバIC24は、表示データRAM1 60を3ポートのメモリセルで構成することによって、静止画データおよび動画 データの別系統による書き込みを可能にしていたが、これに限定されるものではない。

# [0122]

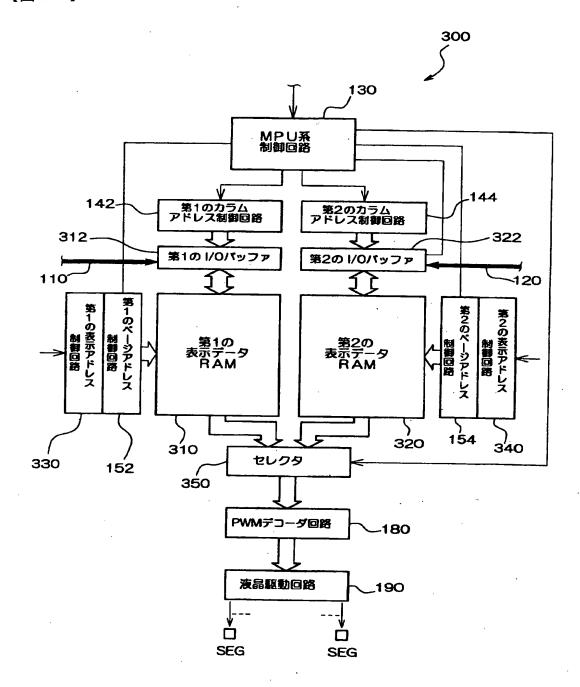

図12は、本発明の第2の実施の形態に係るXドライバIC300の一部のブロック図である。なお、図12において図4と同一機能を有する回路については、図4と同一の符号を用いその詳細な説明を省略する。また、図12にて省略されている回路は、図4の回路と同一である。

#### [0123]

図12に示すXドライバIC300が図4に示すXドライバIC24と相違する点は、まず第1,第2の表示データRAM310,320を設けた点である。第1の表示データRAM310には静止画データが記憶され、第2の表示データRAM320には動画データが記憶される。なお、第1,第2のRAM310,320は、図6に示す第2のワード線W2と、第2のビット線対B2,/B2と

、第2のカラムスイッチSW2と、第2のカラムアドレスデコーダ144Aと、 第2のページアドレスデコーダ154Aは不要であり、従来構成のメモリセルを 用いることができる。

#### [0124]

図13は、第1の表示データRAM310の静止画表示領域310、第2の表示データRAM320の動画記憶領域320A、液晶パネル22の動画表示領域22Aおよび静止画表示領域22Bの関係を示している。

# [0125]

第1,第2の表示データRAM310,320は液晶パネル22の一画面の全画素と対応する記憶領域を有する。これにより、図13に示す静止画記憶領域310Aおよび動画記憶領域320Aは任意に変更可能となる。なお、図13では説明の便宜上、第1,第2の表示データRAM310,320の各メモリ空間と、液晶パネル22の表示空間とを同一の大きさに描いている。

# [0126]

例えば1秒間に20枚のフレームレートにて第2の表示データRAM320の動画記憶領域320Aにデータが書き込まれ、例えば1秒間に60枚のフレームレートにてデータが読み出されて液晶パネル22の動画表示領域22Aに表示される。一方、例えば1秒間に90枚のフレームレートにて第1の表示データRAM310の静止画記憶領域310Aにデータが書き込まれ、例えば1秒間に60枚のフレームレートにてデータが読み出されて液晶パネル22の静止画表示領域22Bに表示される。

#### [0127]

このように、第2の実施の形態では第1の実施の形態とは異なり第1,第2の表示データRAM310,320を設けている。このため、第1の表示データRAM310に対応させて、第1のカラムアドレス制御回路142、第1のI/Oバッファ312、第1のページアドレス制御回路152および第1の表示アドレス制御回路330を設けている。同様に、第2の表示データRAM320に対応させて、第2のカラムアドレス制御回路144、第2のI/Oバッファ322、第1のページアドレス制御回路154および第2の表示アドレス制御回路340

を設けている。

[0128]

さらに、第1,第2の表示データRAM310,320からの表示データを、MPU系制御回路130からの出力に基づいて選択してPWMデコーダ回路180に出力するセレクタ350を設けている。

[0129]

本発明の第2の実施の形態においても、静止画、動画は第1,第2のバスライン110,120により別系統にて伝送される。また、第1のRAM310,第2のRAM320にデータを書き込むためのカラムおよびページアドレスも、静止画と動画とで別系統で指定される。このため、動画データを第2のRAM320に書き換えながら、同時に静止画データを第1のRAM310にて書き換えることができ、動画データの書き込みの終了を待って静止画データを書き込む必要がない。

[0130]

なお、本発明は上述した実施の形態に限定されるものではなく、本発明の要旨 の範囲内で種々の変形実施が可能である。

[0131]

また、本発明では、映画情報を提供するコンテンツサービスを受ける電子機器 について説明したが、これに限定されるものではない。

【図面の簡単な説明】

【図1】

本発明が適用される電子機器の概略ブロック図である。

【図2】

図1の電子機器の一例である携帯電話機の概略ブロック図である。

【図3】

図1に示す液晶パネルの表示例とは異なる表示例を示す概略説明図である。

【図4】

図1に示すXドライバ I Cの概略ブロック図である。

【図5】

図4に示す表示データRAM及びその周辺回路の概略説明図である。

【図6】

図5に示す表示データRAM内のメモリセルの回路図である。

【図7】

静止画及び動画の書き込みクロックと表示用読み出しクロックとを示す波形図である。

【図8】

第1の実施の形態に係るXドライバICを備える電子機器としての携帯電話機の一例の構成要部を示すブロック図である。

【図9】

第1の実施の形態に係るXドライバICを備える電子機器としての携帯電話機の表示部の一例を示す説明図である。

【図10】

第1の実施の形態に係る電子機器としての携帯電話機における静止画および動画が混在した画像情報の表示処理の一例の前半部を示す流れ図である。

【図11】

第1の実施の形態に係る電子機器としての携帯電話機における静止画および動画が混在した画像情報の表示処理の一例の後半部を示す流れ図である。

【図12】

本発明の第2の実施の形態に係るXドライバICの概略ブロック図である。

【図13】

図12に示す第1,第2の表示データRAMの記憶領域と液晶パネルの表示領域との関係を示す概略説明図である。

【符号の説明】

- 10 MPU

- 12 CPU

- 14 静止画用メモリ

- 16 DSP (ディジタル・シグナル・プロセッサ)

- 18 動画用メモリ

- 20 表示ユニット

- 22 液晶パネル

- 22A, 262 動画表示領域

- 22B, 260 静止画表示領域

- 24 XドライバIC

- 26 YドライバIC

- 30 携帯電話機

- 32 アンテナ

- 34 変復調回路

- 36 ディジタルビデオカメラ

- 38 操作入力部

- 100 MPUインターフェース

- 102 入出力バッファ

- 104 入力バッファ

- 110 第1のバスライン

- 112 バスホールダ

- 114 コマンドデコーダ

- 116 ステータス設定回路

- 120 第2のバスライン

- 122 バスホールダ

- 130 MPU系制御回路

- 140 カラムアドレス制御回路

- 142 第1のカラムアドレス制御回路

- 142A 第1のカラムアドレスデコーダ

- 144 第2のカラムアドレス制御回路

- 144A 第2のカラムアドレスデコーダ

- 150 ページアドレス制御回路

- 152 第1のページアドレス制御回路

- 152A 第1のページアドレスデコーダ

- 154 第2のページアドレス制御回路

- 154A 第2のページアドレスデコーダ

- 160 表示データRAM

- 162 I/Oバッファ

- 170 ドライバ系制御回路

- 172 Xドライバ系制御回路

- 174 Yドライバ系制御回路

- 176 発振回路

- 178 電源制御回路

- 180 PWMデコーダ回路

- 190 液晶駆動回路

- 200 メモリ素子

- 201, 202 CMOSインバータ

- 204,206 第1,第2の配線

- 210, 212 第1, 第2のN型MOSトランジスタ (第1のスイッチ)

- 220, 222 第1, 第2のP型MOSトランジスタ

- 230, 232 第3, 第4のN型MOSトランジスタ(第2のスイッチ)

- 250 メモリ

- 252 動画領域設定部

- 254 動画データ書込部

- 256 静止画領域設定部

- 258 静止画データ書込部

- 300 XドライバIC

- 310,320 第1,第2の表示データRAM

- 312, 322 I/Oバッファ

- 330,340 第1,第2の表示アドレス制御回路

- 350 セレクタ

- W1~W3 第1~第3のワード線

- B1, /B1 第1のビット線対

## 特2000-211080

B 2, /B 2 第2のビット線対 C 1 0, C 1 1, C 2 0, C 2 1 メモリセル 【書類名】図面【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

## 【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【書類名】

要約書

【要約】

【課題】 RAMへの動画のデータの書き込みと同時に静止画データを書き込む ことができるRAM内蔵ドライバを提供すること。

【解決手段】 RAM内蔵XドライバIC24は、MPU10からの静止画データ、動画データを伝送する第1,第2のバスライン110,112と、静止画データおよび動画データを記憶するRAM160と、静止画データを書き込むためのRAMのカラム・ページアドレスを指定する第1のカラム・ページアドレス制御回路142,152と、動画データを書き込むためのRAMのカラム・ページアドレス制プドレスを指定する第2のカラム・ページアドレス制御回路144,154と、MPUからのコマンドに基づいて、各アドレス制御回路を制御するMPU系制御回路130と、RAMに記憶された静止画データおよび動画データを、表示データとして読み出し制御する表示アドレス制御回路156と、表示アドレス制御回路を制御するドライバ系制御回路170とを有する。

【選択図】

図4

## 認定・付加情報

特許出願の番号 特願2000-211080

受付番号 50000877582

書類名 特許願

担当官 第一担当上席 0090

作成日 平成12年 7月17日

<認定情報・付加情報>

【特許出願人】

【識別番号】 000002369

【住所又は居所】 東京都新宿区西新宿2丁目4番1号

【氏名又は名称】 セイコーエプソン株式会社

【代理人】 申請人

【識別番号】 100090479

【住所又は居所】 東京都杉並区荻窪5丁目26番13号 荻窪TM

ビル2階 井上・布施合同特許事務所

【氏名又は名称】 井上 一

【選任した代理人】

【識別番号】 100090387

【住所又は居所】 東京都杉並区荻窪5丁目26番13号 荻窪TM

ビル2階 井上・布施合同特許事務所

【氏名又は名称】 布施 行夫

【選任した代理人】

【識別番号】 100090398

【住所又は居所】 東京都杉並区荻窪5丁目26番13号 荻窪TM

ビル2階 井上・布施合同特許事務所

【氏名又は名称】 大渕 美千栄

## 出願人履歴情報

識別番号

[000002369]

1. 変更年月日

1990年 8月20日

[変更理由]

新規登録

住 所

東京都新宿区西新宿2丁目4番1号

1

氏 名

セイコーエプソン株式会社